2024年<>月,Moso参加了在美国拉斯维加斯举行的盛大展览,展位上人头攒动。

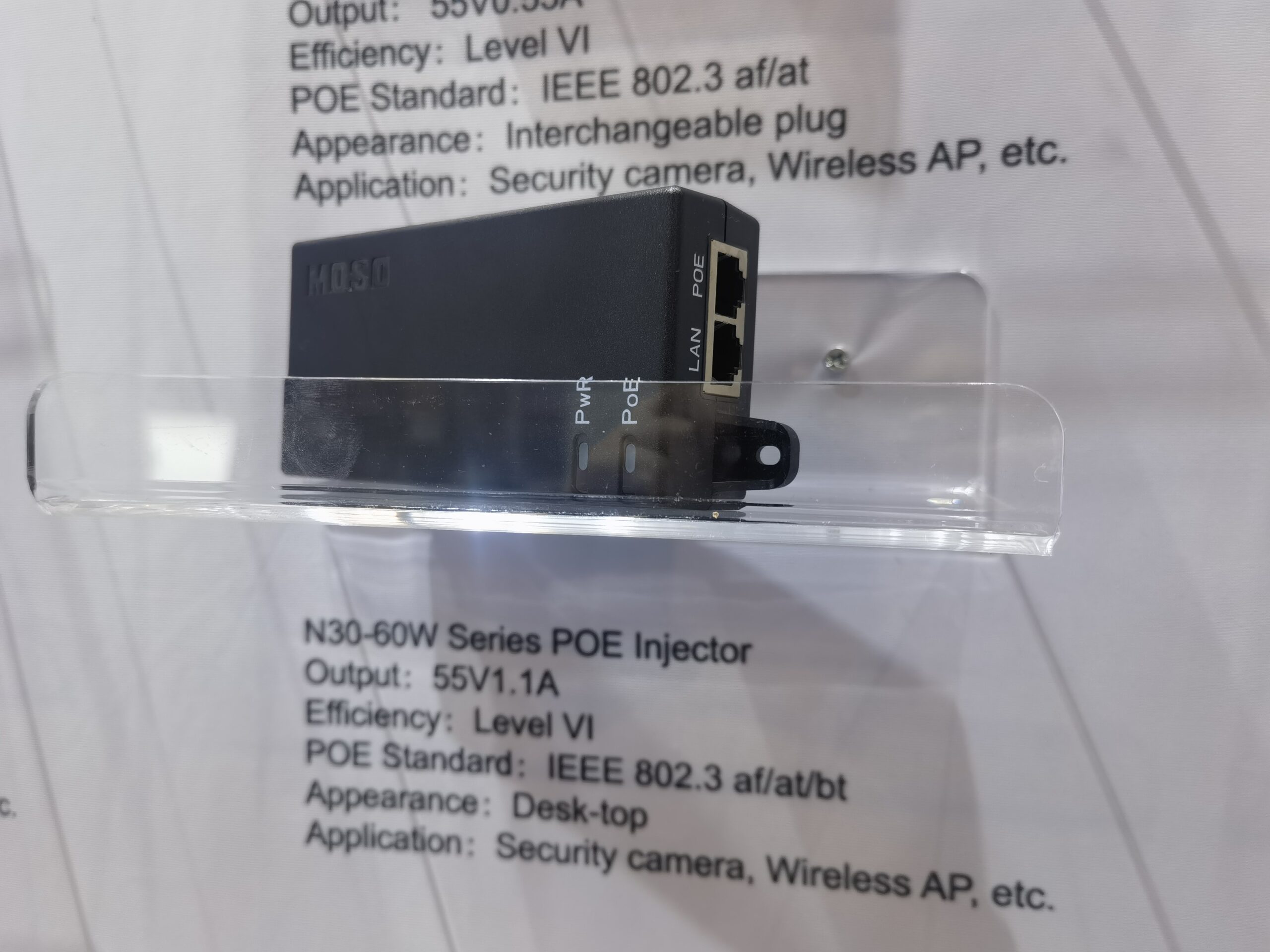

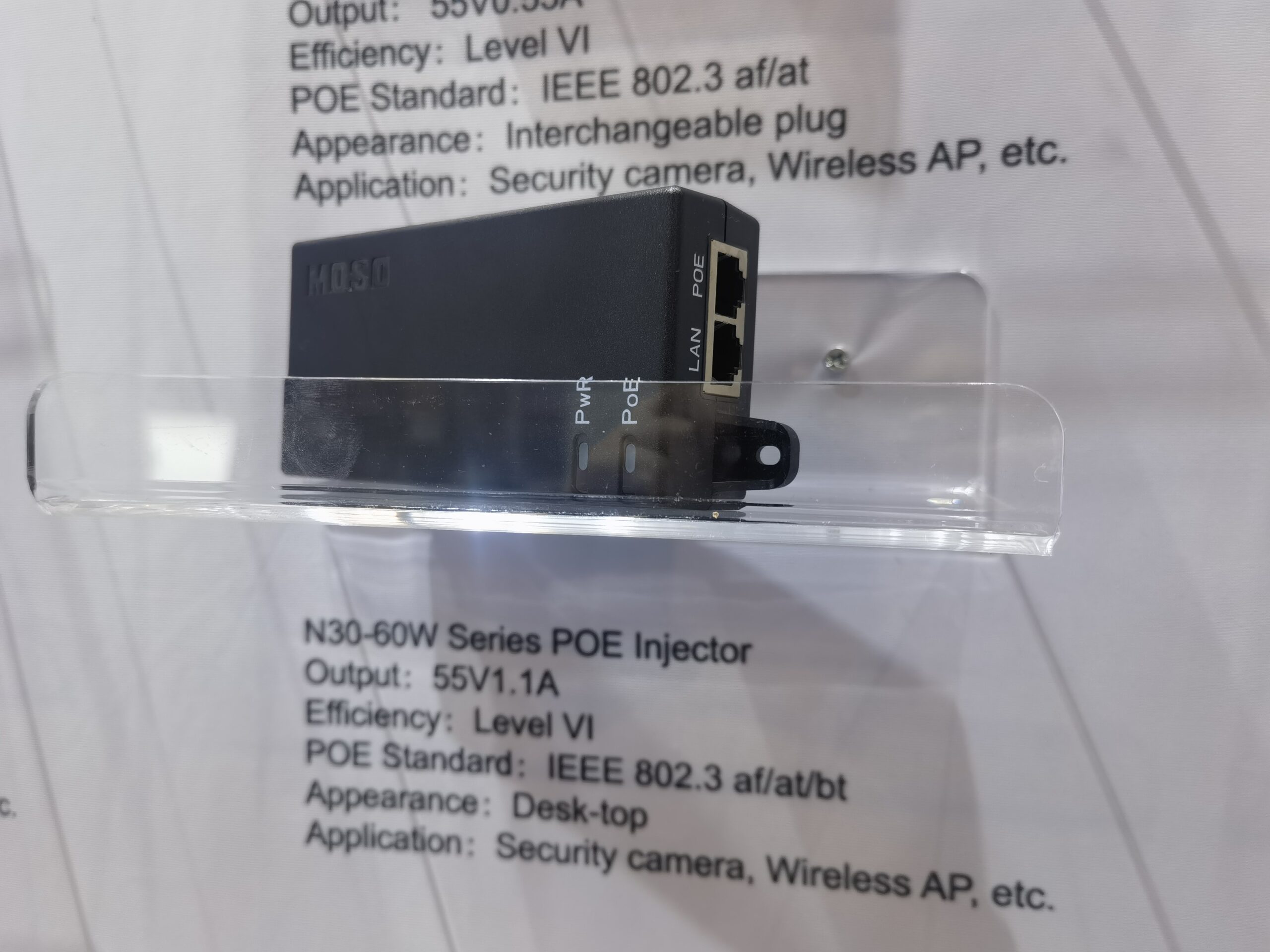

我们展示的适配器系列产品因其效率高、电压稳定、电流充足、多重保护等特点而受到客户的好评。

特别是兼容多协议、高效数据传输的POE产品,赢得了客户的广泛好评。

客户纷纷表示,摩索电源产品性能优异,应用范围广,值得信赖。

本次展会不仅展示了摩硕电源的实力,也加深了与客户的合作关系。未来,我们将坚定不移地坚持客户至上的理念,继续提供更优质的产品和服务!

Founded In

Employees

R&D Patent

Products Cover Area

Headquarters

Headquarters

Headquarters

Headquarters

Cooperative factory

Cooperative factory

Headquarters Production Base

Production Base

Cooperative factory

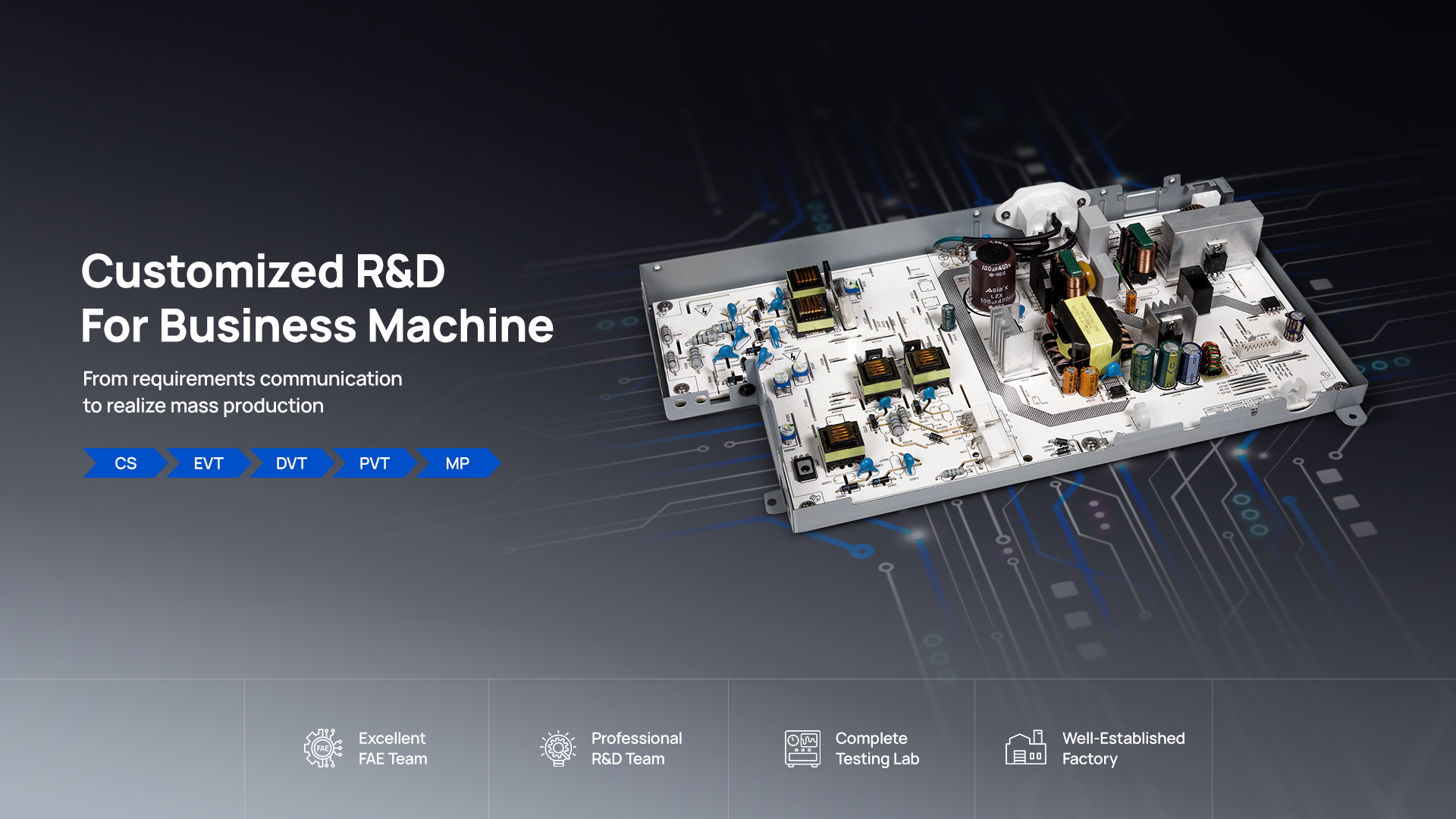

With solid experience in industrial design, MOSO’s R&D team actively develops various intermationally leading innovation technologies and products to provide customers with more efficient and energy-saving solutions .

“Innovative Technology, Product is King”has always been the core value of MOSO technology and MOSO has won the certification of “National High-tech Enterprise” and “Shenzhen High-tech Enterpeise”

MOSO continues to improve product quality, expand production capacity, and reduce costs. In recent years, MOSO has developed and upgraded its automated manufacturing equipment.

MOSO manufacturing has an excellent manufacturing system, with reliable quality and continuous improvement.

2024年<>月,Moso参加了在美国拉斯维加斯举行的盛大展览,展位上人头攒动。

我们展示的适配器系列产品因其效率高、电压稳定、电流充足、多重保护等特点而受到客户的好评。

特别是兼容多协议、高效数据传输的POE产品,赢得了客户的广泛好评。

客户纷纷表示,摩索电源产品性能优异,应用范围广,值得信赖。

本次展会不仅展示了摩硕电源的实力,也加深了与客户的合作关系。未来,我们将坚定不移地坚持客户至上的理念,继续提供更优质的产品和服务!

April 14, 2024

Qorvo’s New 750V Gen 4 SiC FET

Qorvo recently announced its surface-mount TO-leadless (TOLL) package for 750V/5.4mΩ silicon carbide (SiC) field effect transistors (FETs), enhancing the company’s performance and expanding its groundbreaking Gen 4 SiC FETs portfolio. This is the first product in a family of 750V SiC FETs that will be released in the TOLL package with on-resistance ranging from 5.4 mΩ to 60 mΩ. These devices are ideal for space-constrained applications, such as solid-state relays and circuit breakers that can handle 100A and AC/DC power supplies ranging from hundreds to thousands of watts.

With the acquisition of UnitedSiC in October 2021, Qorvo has built a high-performance portfolio of SiC-based FET products, enabling the company to offer power solutions across applications such as power conversion, motion control and circuit protection.

Challenging Applications

The new devices address the size, efficiency and cost of server power supplies, where power density has increased to over 100W/in. This is because the processor consumes a lot of power and requires more power for the same size (>3 kW per AC/DC PSU). Similarly, solid-state circuit breakers require solutions for space-constrained applications where active cooling is an option and can withstand high current and voltage.

Qorvo’s new TOLL package devices fulfil these requirements for the following reasons:

Reduced package footprint

A thinner package allows thicker heat sinks

Low power loss

Adopts surface-mount technology for automated assembly onto PCB daughter boards to reduce costs

Low resistance per package eliminates the need for multiple FETs in parallel

High current carrying capacity and longer short-circuit withstand time

Noise resistance with adequate response time

traditional D3-PAK packages, as shown in Figure 2.

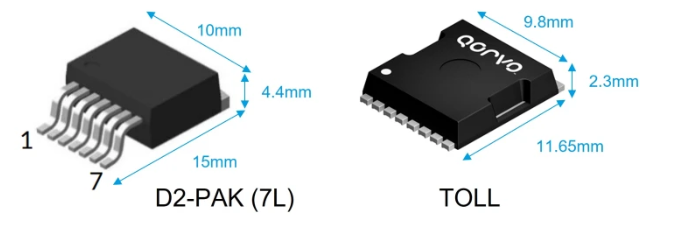

TOLL features reduced footprint and height compared to conventional D2-PAK packages, as shown in Figure 1.

Figure 1: Low R DS(on) Surface Mount Product Dimensions—The D2PAK7L with the TOLL (Qorvo) 4th Generation SiC FET provides unmatched performance in terms of the key figure of merit for RDS(on)

Furthermore, the device has an RDS(on) of 5.4 mΩ in a TOLL package, which is 4 to 10 times lower than GaN transistors, SiC MOSFETs and best-in-class silicon MOSFETs. The SiC FET’s 750V rating is also 100 to 150V higher than other technologies, which significantly improves design margins for handling voltage transients.

As shown in Figure 1, the TOLL package has a 30% smaller footprint and 50% shorter height (2.3 mm) than comparable D2PAK surface-mount alternatives. The TOLL package also features a Kelvin source connection for reliable high-speed switching.

The new SiC FET utilizes Qorvo’s unique cascode circuit configuration, where a SiC JFET is co-packaged with a silicon MOSFET to create a device that takes advantage of the efficiency benefits of wide bandgap switch technology, as well as the simpler gate drive of silicon MOSFETs. SiC JFETs offer the same RDS(on) as SiC MOSFETs, but require a smaller chip area and are usually located on the device. Combining a SiC JFET with a normally-off silicon MOSFET, the cascode circuit configuration retains the benefits of JFET and is compatible with standard SiC MOSFETs. It is a normally-off configuration that is clear to the customer and has a standard three-terminal device with gate, source and drain.

technology and the simpler gate drive of silicon MOSFETs. SiC JFETs provide the same RDS(on) as SiC MOSFETs, but require a smaller chip area and are typically located on the device. Combining SiC JFETs with normally off silicon MOSFETs, the common-source common-gate configuration retains the benefits of JFETs while allowing compatibility with standard SiC MOSFETs. The common-source gate is a normally closed configuration that is transparent to the customer and has a standard three-terminal device with gate, source, and drain.

The new FETs achieve an industry-leading 0.1°C/W thermal resistance from junction to case, despite the size reduction. The new 750V/5.4mΩ UJ4SC075005L8S utilizes an advanced manufacturing process (e.g., sintered chip mount) and features a 120A current rating up to case temperatures of 144°C while the pulsed current rating is 588A up to 0.5ms.

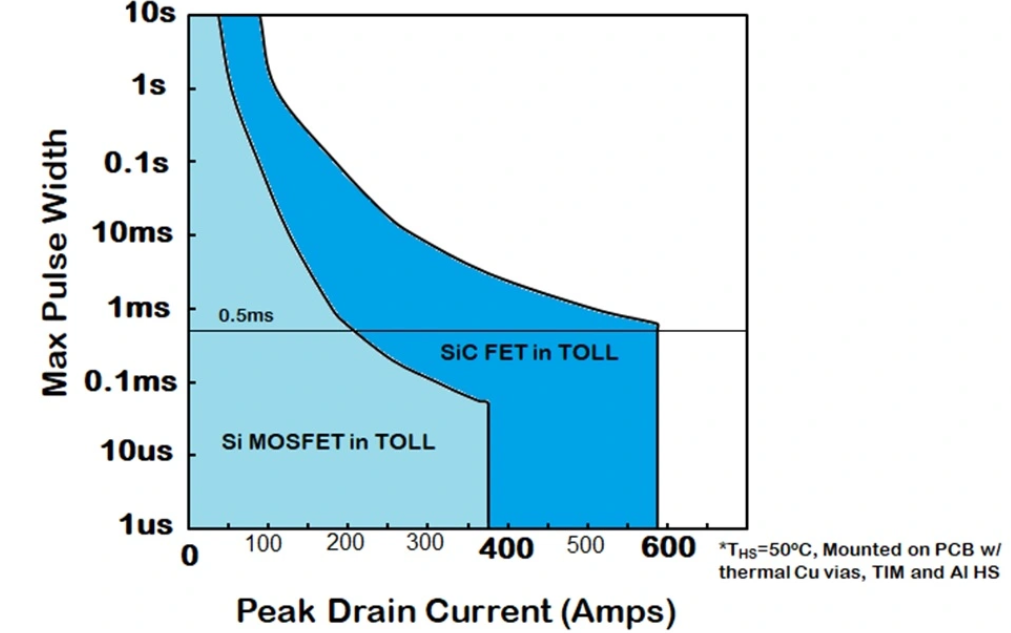

Combined with ultra-low on-resistance, high T j(max) of 175°C and excellent transient thermal behavior, this results in an “I 2 t” rating that is about 8 times better than a silicon MOSFET in the same package, boosting robustness and immunity to transient overloads, while also simplifying the design. Moreover, the overcurrent of the SiC FET is 2.8 times higher than the RDS(on) silicon MOSFET in the same package (tp~0.5-1 ms). This is illustrated in Fig. 2, which shows the pulse current versus pulse width for silicon and SiC FETs in a TOLL package.

Figure 2: Pulse Width vs. (Square) Pulse Current of 750V/5.4mΩ SiC FETs vs. RDS(on) 600V Silicon MOSFETs in TOLL Packages (Qorvo) These new ultra-low RDS(on)

Comparison of pulse width and (square wave) pulse current of a 750V/5.4mΩ SiC FET with a RDS(on) 600V silicon MOSFET in a TOLL package.

These new ultra-low RDS(on) TOLL devices are ideal for applications with thermal challenges in small enclosed locations without active cooling due to low conduction losses, compact size, high surge durability, and excellent shutdown capability as they can reduce heat dissipation and prevent the need for multiple FETs in parallel.

July 21, 2023

sales@mosopower.com

+86 755 2765 7408ㅤ +86 755 2765 3037

+86 159 2067 7370

Moso Industrial Park, Xili Town, Nanshan District, Shenzhen, China(518108)

Hongda (International) Industrial Manufacturing City, Luoyang Town, Boluo County, Huizhou, China(516100)

MOSO Vietnam Electronics Company Limited, Plot D4, Chau Son Industrial Zone, Chau Son Ward, Phu Ly City, Ha Nam Province, Vietnam(18115)

sales@mosopower.com

+86 755 2765 7408ㅤ +86 755 2765 3037

+86 159 2067 7370

Moso Industrial Park, Xili Town, Nanshan District, Shenzhen, China(518108)

Hongda (International) Industrial Manufacturing City, Luoyang Town, Boluo County, Huizhou, China(516100)

MOSO Vietnam Electronics Company Limited, Plot D4, Chau Son Industrial Zone, Chau Son Ward, Phu Ly City, Ha Nam Province, Vietnam(18115)

sales@mosopower.com

+86 755 2765 7408ㅤ +86 755 2765 3037

+86 159 2067 7370

Moso Industrial Park, Xili Town, Nanshan District, Shenzhen, China(518108)

Hongda (International) Industrial Manufacturing City, Luoyang Town, Boluo County, Huizhou, China(516100)

MOSO Vietnam Electronics Company Limited, Plot D4, Chau Son Industrial Zone, Chau Son Ward, Phu Ly City, Ha Nam Province, Vietnam(18115)